Phagwara, India

Venkatesham Maddela<sup>1</sup>, Sanjeet Kumar Sinha<sup>2</sup>, Muddapu Parvathi<sup>3</sup> and Vinay Sharma<sup>4</sup>.

<sup>1,3</sup>Department of Electronics and Communication Engineering, BVRIT HYDERABAD College of Engineering for Women, Hyderabad, India

<sup>4</sup>ni2designs Pvt.Ltd, Pune, India.

E-mail: <u>mvenkateshkp@gmail.com<sup>1</sup></u>, <u>sanjeetksinha@gmail.com<sup>2</sup></u>, <u>pbmuddapu@gmail.com<sup>3</sup></u>, vinay@ni2designs.com<sup>4</sup>.

#### Abstract

The technology advances from the micron level to the Nanometer level. This striking change in the technology with so many factors might influence the embedded device design and its performance. In the fast-growing technology, it is very difficult to find suitable test method to test embedded SRAM. It is noticed that while going to deep sub-nano technologies, the existing test methods may not fully satisfy the test results due to the increased number of faults and defects. Scale-down technologies have an impact on the parasitic effects also, the parasitic effect creates an additional source of faulty behavior, and making the existing test techniques less effective in detecting them. In this paper we propose a method, taking the parasitic effect into the consideration, which gives the fault information along with its location. In the proposed method we have considered node-to-node open and short defects for different technologies (45nm, 32nm, and 7nm). It is observed that using the proposed test method we have detected existing faults and also undefined faults.

Key Words: Open Faults; Short Faults; Parasitic Extraction Method, Undefined short fault.

#### **1.** Introduction

After the invention of integrated circuits in 1949, technology advanced rapidly, integration changed from small-scale integration to very large-scale integration, and the transistor count increased from tens to ten billion. As technology advances, the feature size decreases. This makes the physical verification and electrical verification more complex and also more critical throughout the design process.

The impact of the circuit's physical malformation on the circuit characteristics can be called a fault. Earlier memory test challenges were few because the size and usage of memory was less. The algorithms written for testing were developed with a mathematical base, but given less importance for their practical usage. Later on, the fault models and test algorithms were developed based on physical defects [1].

Memory tests are performed to confirm the correct functioning of a memory device. Various test methodologies have been implemented to identify memory defects. Traditional test methods are zero/one, checkerboard, GALPAT, walking 1/0, and sliding diagonal to name a

Volume 26 Issue 01, 2023

ISSN: 1005-3026

COMPARATIVE ANALYSIS OF OPEN AND SHORT DEFECTS IN EMBEDDED SRAM USING PARASITIC EXTRACTION METHOD FOR DEEP SUBMICRON TECHNOLOGY.

https://dbdxxb.cn/

few[2]. Initially, investigations were carried out based on fault and fault modeling. The majority of the test methodologies are based on the type of fault that occurs in the memory. The eSRAM fault is defined as the representation of a physical defect at the proper level of abstraction [3]. For ensuring the SRAM operating correctly different testing methods are used. March tests are most common methods used to test memories on SoC, but all March Tests cannot detect all the faults. For example March C- and March2 test methods cannot detect faults like Write Destructive faults (WDF) and Deceptive Read Destructive Faults (DRDF), whereas March CL can detect only DRDF0 and March SR can detect only DRDF faults. March SS (22N), March MSS(18N) detect all unlinked faults[4-6].

Quiescent current ( $I_{DDQ}$ ) test also used to test the SRAM Cell. But detection of all faults not possible using the  $I_{DDQ}$  test because for nanometer technologies the variation in current is very less [7]. Due to scale down technologies, and memory size physical examination of the SRAM is not possible. As a result, the testing process is based on a comparison of the logical behavior of good and faulty memories. The most common faults occur in SRAM is Open and bridging faults.

March tests are most commonly used to test embedded memory. These test are designed to test static faults. There are other type of faults which are most difficult to test the memories. These faults are known as dynamic faults. Dynamic faults requires more than one operation to sensitize an issue. M. Sachdev concentrate on open and resistive open faults that could occur in address decoders among the known dynamic faults [8]. Scale-down technologies also influence parasitic parameters like capacitance and resistance. This parasitic effect causes additional faults, which are not detected by the existing test methods like March Tests, I<sub>DDQ</sub> tests etc. Resistive-opens/shorts faults are timing-dependent fault models. Furthermore, it is important to consider resistive open faults become important because of the increased number of interconnection layers in contemporary technologies

The rest of the paper is organized as follows: Section II shows the existing method. This section summarizes the steps involved in the proposed method and also testing of short faults. In Section III, the development of proposed method for deep sub-Nano technology for open and short faults. Section IV discusses the detection of the both defined and undefined faults. Section V concludes this paper.

### **2.** Existing Method:

Now a day's technology advances towards miniaturization, high error-prone designs may result in dense eSRAMs. This causes a reduction in memory and SoC yield. Thus, some sort of solution is required, that should be free from technology variations as well as independent of the fault chosen. Parvathi at.al. Proposed a new parasitic extraction method that gives fault coverage with fault location [9, 10]. The latest testing technique does not consider the impact of the parasitic memory effect for sub-nano meter technology, this is another drawback, which results in an incomplete test. Aiming this we proposed a testing method for eSRAM using parasitic R, C extraction from a fault-induced layout, which gives an extreme fault detection for sub nano meter technology.

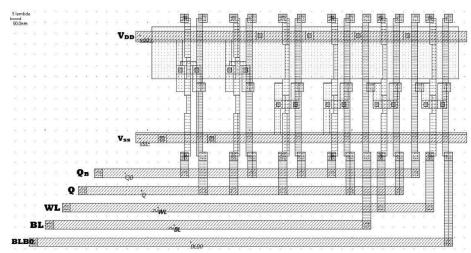

Fig 1. Layout Diagram of 6T SRAM

As shown in fig. 1, in 6T SRAM layout contains seven nodes (Q, QB, WL, BL, BLB, VDD, and VSS). In the proposed method, parasitic R, and C values are observed at each individual node (Q, QB, BL, BLB, and WL). On selecting a particular node, it gives the total parasitic R, and C values at that node. Parasitic capacitance is a combination of metal capacitance, cross-talk capacitance, diffusion capacitance, and gate capacitance. Similarly, parasitic resistance comprises metal resistance, poly resistance, via resistance, and diffusion resistance.

In the Parasitic Extraction Method, initially, we extract the R and C values at each node. Later we impose the short/open between each node and then extract the R, C values at each node, these extracted values are compared with the R, C values of fault-free SRAM cell. The deviation between the extracted R and C values of the faulty and fault-free cell indicates the fault at the node. Hence the following steps are involved in the parasitic extraction method. i) model the circuits with fault imposed ii) categorize the fault types iii) Get the fault model circuit's defect-induced layout out and check for wire shorts, open circuits, or missing wires. iv) Collect parasitic R and C samples from every faulty layout, and compare them with a prototyped fault-free layout. Implemented the proposed parasitic extraction method for short/bridge faults for the 180nm, 120nm and 90nm technologies. In this paper we have consider both open faults and short faults for the sub nano mater technologies upto the 7nm technology.

### 3. Proposed Fault Model with short/open defects in single cell SRAM

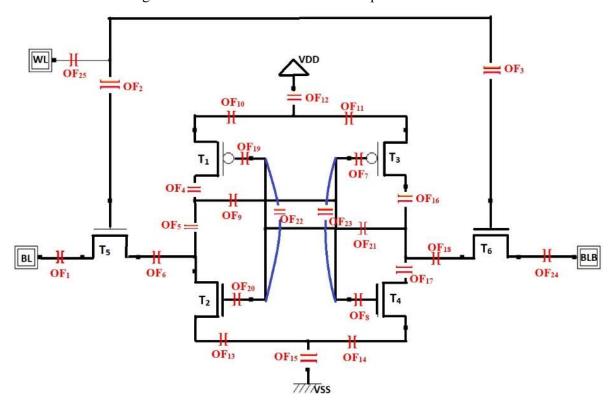

Several open and short faults are analyzed in the proposed method. Fig 2 and Fig.3 depict the scheme of 6T-SRAM cell with all possible open and Short Defects Fig 2: 6T-SRAM Cell fault model for Open Faults

Fig.1 shows 6T SRAM cell with seven main nodes Q, QB, BL, BLB, WL, VDD, and VSS. Out of which Q and QB are internal nodes through them the cell state can be monitored and WL, BL and BLB are external nodes through these writing and reading operations can be performed. The VDD and VSS are supply and ground nodes respectively.

| Table 1. Shows the node equivalence corresponding to main r |                                    |  |  |  |  |  |

|-------------------------------------------------------------|------------------------------------|--|--|--|--|--|

| Node                                                        | Node Equivalence                   |  |  |  |  |  |

| Q                                                           | $M_2D, M_1D, M_5D, M_3G, M_4G$     |  |  |  |  |  |

| QB                                                          | $M_3D, M_4D, M_6S, M_2G,$          |  |  |  |  |  |

| WL                                                          | M <sub>5</sub> G, M <sub>6</sub> G |  |  |  |  |  |

| BL                                                          | M <sub>5</sub> S                   |  |  |  |  |  |

| BLB                                                         | M <sub>6</sub> D                   |  |  |  |  |  |

| VDD                                                         | $M_2S, M_3S$                       |  |  |  |  |  |

| VSS                                                         | $M_1S, M_4S$                       |  |  |  |  |  |

|                                                             | Q<br>QB<br>WL<br>BL<br>BLB<br>VDD  |  |  |  |  |  |

| Table 1 | . Shows | the node | equivalence | e corresponding | to main nodes. |

|---------|---------|----------|-------------|-----------------|----------------|

|         |         |          |             |                 |                |

Internal node Q is a common point to drain  $M_1$  ( $M_1D$ ),  $M_2$  ( $M_2D$ ), and  $M_5$  ( $M_5D$ ) transistors. It is also the common point for the gate of  $M_3$  ( $M_3G$ ) and  $M_4$  ( $M_4G$ ) transistors. Hence short between  $M_1D$  to QB is equivalent to a short between Q and QB. It is true with other equivalent nodes. Including equivalent nodes, all possible short defects between the internal and external nodes are 259. However, excluding equivalent nodes, the actual short defects found are only 21. For simplicity, the short defects are represented with SD (abbreviation for Short Defects) listed in table 2.

|      |                         | Short            | rt Technology |                          |                 |  |  |  |

|------|-------------------------|------------------|---------------|--------------------------|-----------------|--|--|--|

| S.No | Fault<br>Representation | between<br>Nodes | 45nm          | 32nm                     | 7nm             |  |  |  |

| 1    | $SD_1$                  | Q-QB             | UWF, URF      | USWF, URF                | USWF,<br>URF    |  |  |  |

| 2    | SD <sub>2</sub>         | WL-BL            | SA1           | TF                       | WBAF, TF        |  |  |  |

| 3    | SD <sub>3</sub>         | WL-BLB           | USF           | USRF-1                   | WBAF,<br>USRF-1 |  |  |  |

| 4    | SD <sub>4</sub>         | WL-VDD           | Error(NAF)    | Error                    | Error           |  |  |  |

| 5    | SD <sub>5</sub>         | WL-VSS           | Error(NAF)    | Error                    | Error           |  |  |  |

| 6    | $SD_6$                  | WL-Q             | SA0, URF      | SA0, URF                 | SA0, URF        |  |  |  |

| 7    | SD <sub>7</sub>         | WL-QB            | SA1,URF       | SA1, URF                 | SA1, URF        |  |  |  |

| 8    | SD <sub>8</sub>         | VDD-<br>VSS      | UWF, URF0     | UWF, URF0                | UWF,<br>URF0    |  |  |  |

| 9    | SD9                     | Q-VDD            | URF, UWF      | URF0, UWF0               | URF0,<br>UWF0   |  |  |  |

| 10   | SD <sub>10</sub>        | Q-VSS            | URF, UWF      | URF1, UWF1               | URF1,<br>UWF1   |  |  |  |

| 11   | SD11                    | QB-VDD           | IOF           | IOF                      | IOF             |  |  |  |

| 12   | SD <sub>12</sub>        | QB-VSS           | UWF, URF0     | TF, URF0                 | TF, URF0        |  |  |  |

| 13   | SD <sub>13</sub>        | Q-BLB            | URF           | URF                      | URF             |  |  |  |

| 14   | SD <sub>14</sub>        | QB-BLB           | WBAF          | WBAF,<br>USWF0,<br>USRF0 | USWF0,<br>USRF0 |  |  |  |

| 15   | SD <sub>15</sub>        | Q-BL             | SA0(WBAF)     | WBAF, SA0                | SA0             |  |  |  |

| 16   | $SD_{16}$               | QB-BL            | USWF,<br>USRF | USWF, USWF               |                 |  |  |  |

| 17   | SD <sub>17</sub>        | BL-BLB           | USWF,<br>USRF | USWF, USRF               | USWF,<br>USRF   |  |  |  |

| 18   | SD <sub>18</sub>        | BL-VDD           | Error(NAF)    | Error(NAF)               | Error(NAF)      |  |  |  |

| 19   | SD19                    | BL-VSS           | Error(NAF)    | Error(NAF)               | Error(NAF)      |  |  |  |

| 20   | SD <sub>20</sub>        | BLB-<br>VDD      | Error(NAF)    | Error(NAF)               | Error(NAF)      |  |  |  |

|    |           |         | _          |            |            |  |

|----|-----------|---------|------------|------------|------------|--|

| 21 | $SD_{21}$ | BLB-VSS | Error(NAF) | Error(NAF) | Error(NAF) |  |

Similarly, there is a possibility to get the open between the two nodes which causes fault in the memory [11-15]. As shown in fig. 2. We analyzed the SRAM cell for open faults for sub nano technology. We found totally 25 open faults defects by excluding equivalent faults. The analysis of open faults and different types of faults observed at each node is shown in table3. Open Faults are represented with OF (abbreviation for Open Fault).

| Defect           |                                      | Techr      | ology     |

|------------------|--------------------------------------|------------|-----------|

| Representation   | Open Defect<br>at nodes              | 7nm        | 32nm      |

| OF <sub>1</sub>  | BL-T <sub>5</sub> S                  | NAF        | NAF       |

| OF <sub>2</sub>  | WL-T <sub>5</sub> G                  | NAF        | NAF       |

| OF <sub>3</sub>  | WL-T <sub>6</sub> G                  | URF        | URF       |

| OF <sub>4</sub>  | Q-T <sub>1</sub> D                   | UWF1       | UWF1      |

| OF <sub>5</sub>  | Q-T <sub>2</sub> D                   | UWF0       | UWF0      |

| OF <sub>6</sub>  | $Q-T_1DT_2D$                         | NAF        | NAF       |

| OF <sub>7</sub>  | Q-T <sub>3</sub> G                   | UWF0, URF0 | TF        |

| OF <sub>8</sub>  | Q-T <sub>4</sub> G                   | UWF1, URF1 | TF        |

| OF <sub>9</sub>  | Q-T <sub>3</sub> GT <sub>4</sub> G   | NAF        | NAF       |

| OF <sub>10</sub> | VDD-T <sub>1</sub> S                 | UWF1       | UWF1      |

| OF <sub>11</sub> | VDD-T <sub>3</sub> S                 | UWF0, URF0 | TF        |

| OF <sub>12</sub> | VDD-T <sub>1</sub> ST <sub>3</sub> S | UWF,URF0   | UWF,URF0  |

| OF <sub>13</sub> | VSS-T <sub>2</sub> S                 | UWF0       | UWF0      |

| OF <sub>14</sub> | VSS-T <sub>4</sub> S                 | UWF1, URF1 | TF        |

| OF <sub>15</sub> | VSS-T <sub>2</sub> ST <sub>4</sub> S | UWF, URF1  | UWF, URF1 |

| OF <sub>16</sub> | QB-T <sub>3</sub> D                  | UWF0, URF0 | TF        |

| OF <sub>17</sub> | QB-T <sub>4</sub> D                  | UWF1,URF1  | UWF1,URF1 |

| OF18             | QB-T <sub>3</sub> DT <sub>4</sub> D  | URF, UWF0  | URF0, UWF |

| OF <sub>19</sub> | QB-T <sub>1</sub> G                  | UWF1       | UWF1      |

| OF <sub>20</sub> | QB-T <sub>2</sub> G                  | UWF0       | UWF0      |

| OF <sub>21</sub> | QB-T <sub>1</sub> GT <sub>2</sub> G  | UWF        | UWF       |

| OF <sub>22</sub> | T <sub>1</sub> G-T <sub>2</sub> G    | UWF        | UWF       |

| OF <sub>23</sub> | T <sub>3</sub> G-T <sub>4</sub> G    | NAF        | NAF       |

| OF <sub>24</sub> | BLB-T <sub>6</sub> S                 | URF        | URF       |

| OF <sub>25</sub> | WL-T <sub>5</sub> GT <sub>6</sub> G  | NAF        | NAF       |

| Table 3  | 6T S | RAM   | Cell one | n defect | list for   | different | technologies |

|----------|------|-------|----------|----------|------------|-----------|--------------|

| Table 5. | 01.0 | IVUIN | CCH OPC  |          | . 1151 101 | uniterent | teennoiogies |

The functional Fault model is the difference between the observed and expected fault model. To detect the fault, we use fault primitives (FPs). The faults detected by using FPs are called detectable faults. There are some faults, which cannot detect by using fault primitives. These faults are called undetectable faults. By using the proposed method, we can detect both faults.

Using the proposed Parasitic R, C method, existing faults identified are Undefined Read and

Write faults( URF, UWF), Transition Faults(TFs), Stuck at Faults(SAFs), Write Before Access Faults (WBAF), Un stabilized Read and Write Faults (USRF, USWF), No Access Faults(NAFs), in addition to these faults we identified a new fault, named as Undefined Short Fault (USF). We also observed that the fault behavior of the cell changed, when technology changed.

### **Stuck at Faults:**

Fig .4: simulation results for SA-0 Faults

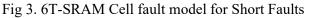

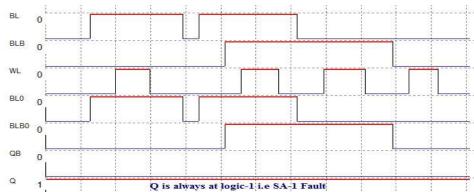

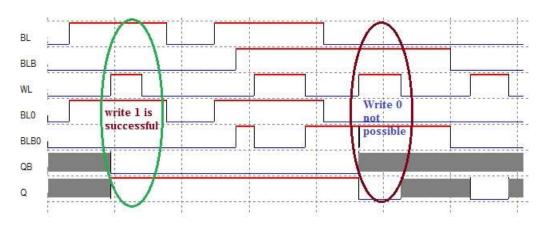

If the cell sticks at a given value for all performed operations. These faults are known as stuckat faults. There are two types of stuck-at faults Stuck at Zero (SA-0) and Stuck at One (SA-1). SA-0 fault occurs when the output is always connected to the ground. We can observe this fault at SD-6(short between the nodes WL-Q), SD<sub>10</sub> (short between the nodes Q-VSS), and SD<sub>15</sub> (short between the nodes Q -BL). SA-1 occurs when output is always connected to VDD). We can observe this fault at SD<sub>2</sub> (When WL-BL shorted), SD<sub>7</sub> (WL-QB shorted), and SD<sub>12</sub> (QB-VSS shorted)

### Fig .5: simulation results for SA-1 Faults

**Transition Faults:** A '0' should be allowed to be entered in a cell that has a '1' stored in it, and vice versa. However, TF appears if the cell doesn't make a transition from its first stored value. In the proposed method TF happens for open defect faults at nodes  $OF_7$ ,  $OF_8$ ,  $OF_{11}$ ,  $OF_{14}$ , and  $OF_{16}$  as shown in table 3.

Fig.6. Simulation results for TF

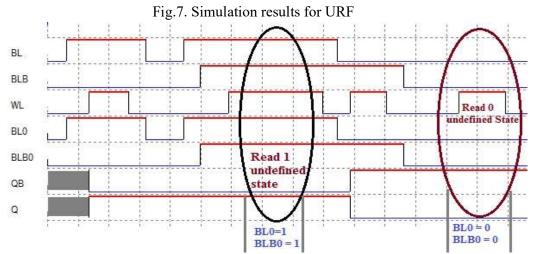

### **Undefined Read Fault:**

For the read operation if the cell goes to the undefined state, the cell is said to have an undefined read fault, Undefined means, the cell state goes to neither '1' nor '0' with the read operation. This fault observed for

the short defect at  $SD_1$ ,  $SD_6$ ,  $SD_7$ ,  $SD_8$ ,  $SD_9$ ,  $SD_{10}$ ,  $SD_{12}$ , and  $SD_{13}$  and for open defects fault induced at  $OF_3$ ,  $OF_{15}$ ,  $OF_{17}$ ,  $OF_{18}$  and  $OF_{24}$ .

For proper Read-1 operation, when we will make Bit Lines BL=1, BLB=1, and when we will enable the write line, we need to get BL0=1 and BLB0=0, but as shown in fig.8, for Read-1 operation we are getting BL0=1 and BLB0=1. This indicates the undefined state. The same operation we can observe for the Read-0 operation

### **Undefined Write Fault:**

An undefined Write Fault is defined as the cell going to the undefined state, when we will perform the write operation of the cell. UWF fault identified for the short faults induced at  $SD_1$ ,  $SD_8$ ,  $SD_9$ ,  $SD_{11}$ , and for the open faults this fault identified at  $OF_4$ ,  $OF_5$ ,  $OF_{10}$ ,  $OF_{12}$ ,  $OF_{13}$ ,

$OF_{15}$ ,  $OF_{17}$ ,  $OF_{19}$ ,  $OF_{20}$ ,  $OF_{21}$  and  $OF_{22}$ . Where SD represents Short Faults and OF represents Open Faults.

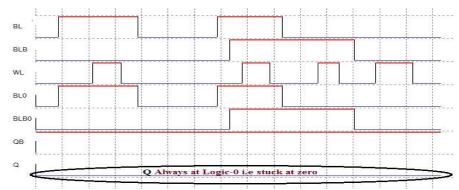

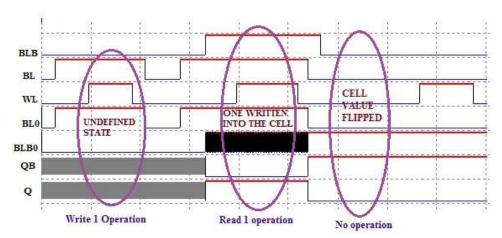

### **Undefined Short Fault:**

An undefined short fault occurs when we introduce a short between the nodes WL-BLB. As shown in fig.8 for the fault defect at WL-BLB, the cell goes to the undefined state for the write 1 operation, it stores logic 1 automatically for the read operation after that the cell value is flipped from logic 1 to logic 0 when we will set the bit line values to zero. This type of fault is not defined by any fault primitive, hence it is observed as a new fault and named an Undefined Short fault.

Fig. 8. Undefined Short Fault at nodes WL-BLB

## 4. Results and Comparison

For the design of embedded SRAM, three technologies have been selected 45nm, 32nm, and 7nm technologies. Table 4. gives the comparison and the overview of the key parameters like supply voltage, delays, current, and length and width of the transistors for the different technology nodes. In the analysis of the parameters, we have considered three modes of operation, Standard, High Voltage, and High Speed. For example in the calculation of delays Tdelay represents standard time delay, the delay represents the delay in high voltage mode and THs represent high-speed mode.

| Parameter      | 180nm | 120nm | 90nm  | 65nm  | 45nm   | 32nm   | 14nm   | 7nm    |

|----------------|-------|-------|-------|-------|--------|--------|--------|--------|

| VDD(V)         | 2     | 1.2   | 1     | 1     | 1      | 1      | 0.8    | 0.8    |

| Tdelay(ns)     | 0.03  | 0.03  | 0.005 | 0.005 | 0.003  | 0.0025 | 0.0016 | 0.0012 |

| THvDelay(ns)   | 0.1   | 0.06  | 0.02  | 0.01  | 0.008  | 0.007  | 0.007  | 0.004  |

| THsDelay(ns)   | 0.6   | 0.02  | 0.004 | 0.003 | 0.002  | 0.002  | 0.005  | 0.002  |

| TWireDelay(ns) | 0.1   | 0.07  | 0.005 | 0.002 | 0.0015 | 0.0014 | 0.001  | 0.001  |

| Tcurrent(mA)   | 0.6   | 0.5   | 0.1   | 0.1   | 0.08   | 0.07   | 0.03   | 0.04   |

| ML(um)         | 0.18  | 0.12  | 0.1   | 0.07  | 0.05   | 0.03   | 0.016  | 0.007  |

| MHvL(um)       | 1.5   | 0.36  | 0.3   | 0.2   | 0.18   | 0.036  | 0.01   | 0.01   |

Table 4. Comparison of Transistor Parameter for different technologies

| MNW(um) | 1.5 | 1 | 0.5 | 0.3 | 0.3 | 0.08  | 0.048 | 0.024 |

|---------|-----|---|-----|-----|-----|-------|-------|-------|

| MPW(um) | 1.5 | 2 | 1   | 0.5 | 0.5 | 0.108 | 0.048 | 0.024 |

The numbers 180nm, 120nm, 90nm, 65nm, 45nm, 32nm, 14nm, and 7nm are representing the minimal channel length that can be fabricated.

The comprehensive fault model dictionary with all three technologies with a list of short defects and corresponding fault models for a single-cell SRAM is shown in table 2.

It is found that few short defects are exhibiting the same faulty behavior in all three technologies chosen. For example, defect models VDD-VSS represent UWF and URF faults. The UWF Fault occurs with a write operation and the same fault model exhibits URF faults with a read operation. This is due to the fault model VDD being shorted to VSS, then which makes the VDD to the ground potential, hence inverter transistors M<sub>1</sub> and M<sub>3</sub> always stay ON position, leading Q and QB always remain at "0". Hence while writing "1" or writing "0", the node Q and QB will be inactive for accepting new values. For read '0', both BL and BLB results with '0' cause an Undefined Read Fault (URF). The same is true for read operation QB.

Apart from the existing faults, few undetectable faults are identified. For example, defect model WL-BLB for 45nm technology results in **Undefined Short Faults**, however, the same defect model is observed as an Unstabilized Read Fault in 32nm technology, and Write before Access Faults and Unstabilized Read fault for 7nm technology.

Similarly, WL-BL behaves as Stuck at Faults in 45nm, but in the other two technologies, it behaves as Transition faults (TF) and Write Before Access Faults (WBAF). Fault models QB-VSS, WL-BLB follow the same.

Table 5. Displays the retrieved parasitic R and C values for three different technologies of faultfree SRAM. Additionally, these values are used in comparison with problematic SRAM cell parasitic for fault detection.

| Input- | Fault free SRAM Cell Parasitic R, C values |       |             |       |             |       |  |  |

|--------|--------------------------------------------|-------|-------------|-------|-------------|-------|--|--|

| output | 45                                         | nm    | 32          | nm    | 7n          | ım    |  |  |

| nodes  | $R(\Omega)$                                | C(aF) | $R(\Omega)$ | C(aF) | $R(\Omega)$ | C(aF) |  |  |

| Q      | 6881                                       | 1900  | 677         | 1800  | 433         | 2900  |  |  |

| QB     | 7585                                       | 1800  | 497         | 1500  | 1170        | 3100  |  |  |

| WL     | 4712                                       | 663   | 421         | 791   | 180         | 1800  |  |  |

| BL     | 1216                                       | 664   | 75          | 701   | 158         | 1100  |  |  |

| BLB    | 240                                        | 354   | 79          | 637   | 54          | 783   |  |  |

| VDD    | 6600                                       | 1900  | 31          | 313   | 2071        | 2700  |  |  |

| VSS    | 2823                                       | 1300  | 13          | 313   | 402         | 1700  |  |  |

Table 5. Parasitic R, C values of Fault Free SRAM Cell for different technologies

|      | Short defect fault model |      |      |      |      |      |      |      |      |      |      |      |

|------|--------------------------|------|------|------|------|------|------|------|------|------|------|------|

|      |                          |      | WL   | -BL  | VDD  | -VSS | QB-V | VDD  | Q-]  | BL   | QB-  | BL   |

| node |                          |      | (WB  | BAF, | (UV  | WF,  | (Io  | F)   | (Sz  | A0)  | (US  | WF,  |

| s    | Fault                    | Free | T    | F)   | UR   | F0)  |      |      |      |      | USI  | RF)  |

|      |                          |      | Effe | cted |

|      |                          |      | No   | de   | No   | de   | No   | de   | No   | ode  | No   | de   |

|      | C(fF                     | R(Ω  | C(fF | R(Ω  | C(fF | R(Ω  | C(fF | R(Ω  | C(fF | R(Ω  | C(fF | R(Ω  |

|      | )                        | )    | )    | )    | )    | )    | )    | )    | )    | )    | )    | )    |

| Q    | 2.9                      | 433  | 2.90 | 433  | 2.90 | 433  | 2.90 | 407  | NA   | NA   | 2.90 | 407  |

| QB   | 3.1                      | 117  | 3.10 | 117  | 3.10 | 117  | NA   | NA   | 3.10 | 117  | NA   | NA   |

|      |                          | 0    |      | 0    | 5.10 | 0    | INA  | INA  | 5.10 | 0    | INA  | INA  |

| WL   | 1.8                      | 180  | NA   | NA   | 1.80 | 180  | 1.80 | 178  | 1.80 | 180  | 1.80 | 180  |

| BL   | 1.8                      | 158  | 1.60 | 236  | 1.10 | 158  | 1.00 | 157  | 2.90 | 529  | 3.50 | 941  |

| BLB  | 0.78                     | 54   | 0.78 | 54   | 0.78 | 54   | 0.75 | 54   | 0.78 | 54   | 0.78 | 54   |

|      | 3                        |      | 3    | 54   | 3    | 54   | 3    | 54   | 3    | 54   | 3    | 54   |

| VD   | 2.7                      | 207  | 2.70 | 207  | 2.40 | 167  | 4.00 | 278  | 2.70 | 207  | 2.70 | 207  |

| D    |                          | 1    | 2.70 | 1    | 2.40 | 0    | 4.00 | 7    | 2.70 | 1    | 2.70 | 1    |

| VSS  | 1.7                      | 402  | 1.70 | 402  | 2.00 | 805  | 1.70 | 402  | 1.70 | 402  | 1.70 | 402  |

| 4.1 Fault Detection | u Using Parasitic R, | C Method for short faults |

|---------------------|----------------------|---------------------------|

|---------------------|----------------------|---------------------------|

Table 6. Variation of parasitic R, C values for SRAM short defect model

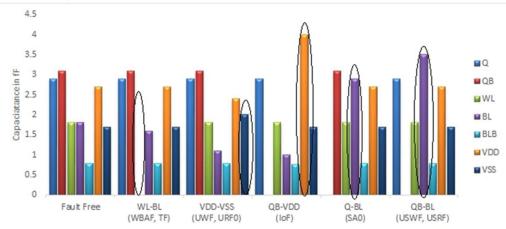

Fig.9 illustrates the fault detection method based on parasitic capacitance change for 7nm technology. Fault model WBAF, TF is created by a short between WL and BL. As expected, parasitic capacitances at other nodes Q, QB, BLB, VDD, and VSS are the same as fault free except at nodes WL and BL, for this fault model node WL is absorbed represented with NA (Node Absorbed).

Fig.9 Fault detection based on parasitic capacitance variation for short defects Similar to the fault model UWF, the parasitic capacitance change is more pronounced at impacting nodes VDD and VSS while remaining the same at other nodes that are fault free. URF0 corresponds to a short defect simulated by the short between VDD and VSS. When QB

is shorted to VDD to simulate a short defect, parasitic variation is seen at VDD, while node QB is absorbed. For the short defect characterized by Q-BL for fault model SA0, The parasitic variation seen at BL and node Q is absorbed.

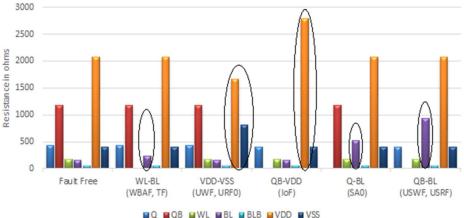

Fig.10. depicts the resistance variation at each node for fault detection. On the graph, X-axis represents the all possible faults, whereas Y-axis represents the resistance in ohms. The same justification applies to fault detection using parasitic resistance

Fig.10 Fault detection based on parasitic resistance variation for short faults The complete fault model dictionary for proposed fault models with parasitic R and C values using 32nm technology for 6T SRAM cell is shown in table 7. The complete fault model dictionary gives all fault model parasitic values taken from nodes Q, QB, BL, BLB, WL, VDD, and VSS. These variations are further compared with fault free. At which node the fault is imposed that corresponding node parasitics are affected in particular with high parasitic R, C variation?

|              | Open<br>Defec<br>t | Node Q<br>Ideal<br>C =<br>2900aF,<br>R=433Ω |          | Nod<br>QB               |                  | Nod<br>WL |         | BL BL                              |         |                                  | Node<br>BLB |                                         | Node<br>VDD |                                        | Node<br>VSS |  |

|--------------|--------------------|---------------------------------------------|----------|-------------------------|------------------|-----------|---------|------------------------------------|---------|----------------------------------|-------------|-----------------------------------------|-------------|----------------------------------------|-------------|--|

| S.<br>N<br>o |                    |                                             |          | Ide<br>C<br>3100<br>R=1 | =<br>)aF,<br>170 | · · · ·   |         | Ideal<br>C =<br>1100 aF,<br>R=158Ω |         | Ideal<br>C =<br>783aF,<br>R= 54Ω |             | Ideal<br>C =<br>2700 aF,<br>R=2071<br>Ω |             | Ideal<br>C =<br>1700 aF,<br>R=<br>402Ω |             |  |

|              |                    | C<br>in                                     | R<br>in  | C<br>in                 | R<br>in          | C<br>in   | R<br>in | C<br>in                            | R<br>in | C<br>in                          | R<br>in     | C<br>in                                 | R<br>in     | C<br>in                                | R<br>in     |  |

|              |                    | aF                                          | Ω        | aF                      | Ω                | aF        | Ω       | aF                                 | Ω       | aF                               | Ω           | aF                                      | Ω           | aF                                     | Ω           |  |

| 1            | Q-QB               | 55<br>00                                    | 15<br>83 | -                       | -                | 18<br>00  | 17<br>8 | 10<br>00                           | 15<br>7 | 75<br>0                          | 53          | 27<br>00                                | 20<br>71    | 17<br>00                               | 40<br>2     |  |

| 2            | WL-<br>BL          | 29<br>00                                    | 43<br>3  | 31<br>00                | 11<br>70         | -         | -       | 16<br>00                           | 23<br>6 | 78<br>0                          | 54          | 27<br>00                                | 20<br>71    | 17<br>00                               | 40<br>2     |  |

| 3            | WL-<br>BLB         | 29<br>00                                    | 43<br>3  | 31<br>00                | 11<br>70         | 21<br>00  | 21<br>9 | 10<br>00                           | 15<br>9 | -                                | -           | 27<br>00                                | 20<br>71    | 17<br>00                               | 40<br>2     |  |

Table 7. Complete Fault Model Dictionary using 32nm Technology for SRAM short defect model

| 4        | WL-<br>VDD  | -        | -       | -        | -        | -        | -        | -        | -       | -       | -  | 28<br>00 | 21<br>64 | 17<br>00 | 40<br>2  |

|----------|-------------|----------|---------|----------|----------|----------|----------|----------|---------|---------|----|----------|----------|----------|----------|

| 5        | WL-<br>VSS  | -        | -       | -        | -        | -        | -        | -        | -       | -       | -  | 27<br>00 | 20<br>71 | 27<br>00 | 55<br>3  |

| 6        | Q-<br>WL    | 40<br>00 | 56<br>5 | 31<br>00 | 80<br>3  | -        | -        | 10<br>00 | 15<br>7 | 75<br>0 | 54 | 27<br>00 | 20<br>71 | 17<br>00 | 40<br>2  |

| 7        | QB-<br>WL   | 29<br>00 | 43<br>3 | -        | -        | 43<br>00 | 13<br>31 | 10<br>00 | 15<br>7 | 75<br>0 | 54 | 27<br>00 | 20<br>71 | 17<br>00 | 40<br>2  |

| 8        | VDD<br>-VSS | 29<br>00 | 43<br>3 | 31<br>00 | 11<br>70 | 18<br>00 | 18<br>0  | 11<br>00 | 15<br>8 | 78<br>0 | 54 | 24<br>00 | 16<br>70 | 20<br>00 | 80<br>5  |

| 9        | Q-<br>VDD   | -        | -       | 30<br>00 | 97<br>1  | 18<br>00 | 17<br>8  | 10<br>00 | 15<br>8 | 78<br>0 | 54 | 36<br>00 | 24<br>09 | 17<br>00 | 40<br>2  |

| 1<br>0   | Q-<br>VSS   | -        | -       | 30<br>00 | 97<br>1  | 18<br>00 | 17<br>8  | 10<br>00 | 15<br>8 | 75<br>0 | 53 | 27<br>00 | 20<br>71 | 31<br>00 | 74<br>3  |

| 1<br>1   | QB-<br>VDD  | 29<br>00 | 40<br>7 | -        | -        | 18<br>00 | 17<br>8  | 10<br>00 | 15<br>7 | 75<br>0 | 54 | 40<br>00 | 27<br>87 | 17<br>00 | 40<br>2  |

| 1<br>2   | QB-<br>VSS  | 29<br>00 | 40<br>7 | -        | -        | 18<br>00 | 17<br>8  | 10<br>00 | 15<br>7 | 75<br>0 | 53 | 27<br>00 | 20<br>71 | 35<br>00 | 11<br>46 |

| $1 \\ 3$ | Q-<br>BLB   | 31<br>00 | 44<br>5 | 31<br>00 | 80<br>3  | 18<br>00 | 18<br>0  | 10<br>00 | 15<br>7 | -       | -  | 27<br>00 | 20<br>71 | 17<br>00 | 40<br>2  |

| 1<br>4   | QB-<br>BLB  | 29<br>00 | 40<br>7 | 34<br>00 | 84<br>2  | 18<br>00 | 18<br>0  | 10<br>00 | 15<br>7 | -       | -  | 27<br>00 | 20<br>71 | 17<br>00 | 40<br>2  |

| 1<br>5   | Q-BL        | NA       | N<br>A  | 31<br>00 | 11<br>70 | 18<br>00 | 18<br>0  | 29<br>00 | 52<br>9 | 78<br>0 | 54 | 27<br>00 | 20<br>71 | 17<br>00 | 40<br>2  |

| 1<br>6   | QB-<br>BL   | 29<br>00 | 40<br>7 | -        | -        | 18<br>00 | 18<br>0  | 35<br>00 | 94<br>1 | 78<br>0 | 54 | 27<br>00 | 20<br>71 | 17<br>00 | 40<br>2  |

| 1<br>7   | BL-<br>BLB  | 29<br>00 | 40<br>7 | 31<br>00 | 80<br>3  | 18<br>00 | 18<br>0  | 13<br>00 | 19<br>6 | -       | -  | 27<br>00 | 20<br>71 | 17<br>00 | 40<br>2  |

| 1<br>8   | BL-<br>VDD  | -        | -       | -        | -        | -        | -        | -        | -       | -       | -  | 28<br>00 | 21<br>98 | 17<br>00 | 40<br>2  |

| 1<br>9   | BL-<br>VSS  | -        | -       | -        | -        | -        | -        | -        | -       | -       | -  | 27<br>00 | 20<br>71 | 18<br>00 | 52<br>8  |

| 2<br>0   | BLB-<br>VDD | -        | -       | -        | -        | -        | -        | -        | -       | -       | -  | 28<br>00 | 21<br>01 | 17<br>00 | 40<br>2  |

| 2<br>1   | BLB-<br>VSS | -        | -       | -        | -        | -        | -        | -        | -       | -       | -  | 27<br>00 | 20<br>71 | 17<br>00 | 43<br>0  |

# 4.2 Fault Detection Using Parasitic R, C Method for Open Faults

Table.8 shows the R, C values of the different fault models, modeled by open faults at each node.

Table 8. Variation of parasitic R, C values for SRAM open defect model

|      | Eault | Enco        | NA    | <b>\</b> F  | UI    | RF          | Т     | F           | UWF       |             |  |

|------|-------|-------------|-------|-------------|-------|-------------|-------|-------------|-----------|-------------|--|

| Node | Fault | Free        | (BL-I | M5S)        | (WL-  | M6G)        | (Q-N  | 13G)        | (M1G_M2G) |             |  |

|      | C(fF) | $R(\Omega)$ | C(fF) | $R(\Omega)$ | C(fF) | $R(\Omega)$ | C(fF) | $R(\Omega)$ | C(fF)     | $R(\Omega)$ |  |

| Q   | 1.7   | 800 | 1.8  | 805 | 1.8  | 813 | 1.6  | 527 | 1.7  | 803 |

|-----|-------|-----|------|-----|------|-----|------|-----|------|-----|

| QB  | 1.5   | 498 | 1.5  | 498 | 1.5  | 498 | 1.5  | 498 | 1.3  | 239 |

| WL  | 0.77  | 296 | 0.78 | 296 | 0.52 | 155 | 0.78 | 296 | 0.78 | 296 |

| BL  | 0.626 | 71  | NA   | NA  | 0.63 | 71  | 0.63 | 71  | 0.63 | 71  |

| BLB | 0.815 | 91  | 0.82 | 91  | 0.82 | 91  | 0.82 | 91  | 0.82 | 91  |

| VDD | 0.31  | 13  | 0.31 | 13  | 0.31 | 13  | 0.31 | 13  | 0.31 | 13  |

| VSS | 0.31  | 13  | 0.31 | 13  | 0.31 | 13  | 0.31 | 13  | 0.31 | 13  |

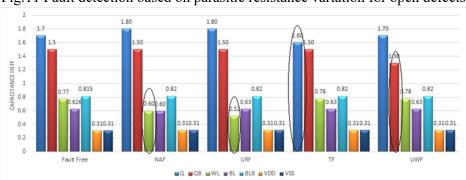

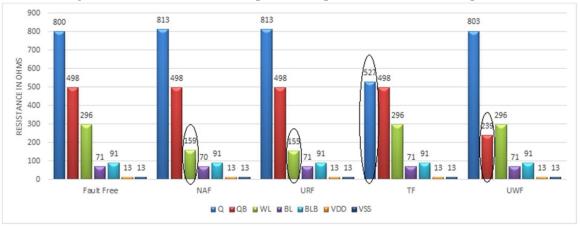

The graphical representation of fault detection using the parasitic R, C extraction method for open faults is shown in Fig 11 and Fig 12. No Access Faults (NAF), arise when we open between the nodes BL and Source of the transistor  $T_5$ , whereas node BL absorbed. For open between node WL and gate of transistor  $T_6$ , causes the fault model Undefined Read Fault (URF), for this fault at node WL the parasitic R, and C values changed to 0.52fF, 1550hms respectively whereas the actual values are 0.77fF, 256 ohms respectively. The explanation is valid and holds for all other faults also.

Fig.11 Fault detection based on parasitic resistance variation for open defects

Fig.12 Fault detection based on parasitic capacitance variation for open defects

Table 9. Complete Fault Model Dictionary using 7nm Technology for SRAM open defects

|          |                | Nod                                | le Q    |                                       | de<br>B |                                      | ode<br>/L | Nod                             | e BL | No<br>BI                         | de<br>LB | No<br>VI                        |    |                                  | ode<br>SS |

|----------|----------------|------------------------------------|---------|---------------------------------------|---------|--------------------------------------|-----------|---------------------------------|------|----------------------------------|----------|---------------------------------|----|----------------------------------|-----------|

| S.<br>No | Open<br>Defect | Ideal<br>C =<br>1.700aF,<br>R=800Ω |         | Ideal<br>C =<br>1500aF,<br>R=498<br>Ω |         | Ideal<br>C =<br>776aF,<br>R=<br>296Ω |           | Ideal<br>C =<br>626aF,<br>R=71Ω |      | Ideal<br>C =<br>815aF,<br>R= 91Ω |          | Ideal<br>C =<br>313aF,<br>R=13Ω |    | Ideal<br>C =<br>313aF,<br>R= 13Ω |           |

|          |                | С                                  | R       | С                                     | R       | C                                    | R         | C                               | R    | С                                | R        | C                               | R  | C                                | R         |

|          |                | in                                 | in      | in                                    | in      | in                                   | in        | in                              | in   | in                               | in       | in                              | in | in                               | in        |

|          |                | fF                                 | Ω       | fF                                    | Ω<br>40 | fF                                   | Ω<br>20   | fF                              | Ω    | fF                               | Ω        | fF                              | Ω  | fF                               | Ω         |

| 1        | BL-M5S         | 1.8<br>0                           | 80<br>5 | 1.5<br>0                              | 49<br>8 | 0.7<br>8                             | 29<br>6   | NA                              | NA   | 0.7<br>7                         | 87       | 0.3                             | 13 | 0.3                              | 13        |

| 2        | WL- M5G        | 1.8<br>0                           | 81<br>3 | 1.5<br>0                              | 49<br>8 | 0.6<br>0                             | 15<br>9   | 0.6                             | 70   | 0.8<br>2                         | 91       | 0.3                             | 13 | 0.3                              | 13        |

| 3        | WL-M6G         | 1.8<br>0                           | 81<br>3 | 1.5<br>0                              | 49<br>8 | 0.5                                  | 15<br>5   | 0.6                             | 71   | 0.8<br>2                         | 91       | 0.3                             | 13 | 0.3                              | 13        |

| 4        | Q-M1D          | 1.4<br>0                           | 68<br>2 | 1.5<br>0                              | 49<br>8 | 0.7<br>8                             | 29<br>6   | 0.6                             | 71   | 0.8<br>2                         | 91       | 0.3                             | 13 | 0.3                              | 13        |

| 5        | Q-M2D          | 1.5<br>0                           | 75<br>5 | 1.5<br>0                              | 49<br>8 | 0.7<br>8                             | 29<br>6   | 0.6                             | 71   | 0.8<br>2                         | 91       | 0.3                             | 13 | 0.3                              | 13        |

| 6        | Q-<br>M1DM2D   | 0.6                                | 80      | 1.5<br>0                              | 49<br>8 | 0.7                                  | 29<br>3   | 0.6                             | 71   | 0.8                              | 91       | 0.3                             | 13 | 0.3                              | 13        |

| 7        | Q-M3G          | 1.6<br>0                           | 52<br>7 | 1.5<br>0                              | 49<br>8 | 0.7<br>8                             | 29<br>6   | 0.6                             | 71   | 0.8<br>2                         | 91       | 0.3                             | 13 | 0.3                              | 13        |

| 8        | Q- M4G         | 1.6<br>0                           | 55<br>1 | 1.5<br>0                              | 49<br>8 | 0.7<br>8                             | 29<br>6   | 0.6<br>3                        | 71   | 0.8<br>2                         | 91       | 0.3<br>1                        | 13 | 0.3<br>1                         | 13        |

| 9        | Q-<br>M3GM4G   | 1.3<br>0                           | 25<br>7 | 1.5<br>0                              | 49<br>8 | 0.7<br>8                             | 29<br>6   | 0.6                             | 71   | 0.8<br>2                         | 91       | 0.3<br>1                        | 13 | 0.3<br>1                         | 13        |

| 10       | VDD-<br>M1S    | 1.7<br>0                           | 71<br>1 | 1.6<br>0                              | 51<br>1 | 0.7<br>8                             | 29<br>6   | 0.6                             | 71   | 0.8<br>2                         | 91       | 0.3                             | 13 | 0.3                              | 13        |

| 11       | VDD-<br>M3S    | 1.8<br>0                           | 81<br>3 | 1.6<br>0                              | 51<br>1 | 0.7<br>8                             | 29<br>6   | 0.6                             | 71   | 0.8<br>2                         | 91       | 0.3                             | 13 | 0.3                              | 13        |

| 12       | VDD-<br>M1SM3S | 1.7<br>0                           | 71<br>1 | 1.6<br>0                              | 51<br>1 | 0.7<br>8                             | 29<br>6   | 0.6                             | 71   | 0.8<br>2                         | 91       | 0.3                             | 13 | 0.3                              | 13        |

| 13       | VSS-M2S        | 1.7<br>0                           | 80<br>0 | 1.6<br>0                              | 51<br>1 | 0.7<br>8                             | 29<br>6   | 0.6                             | 71   | 0.8<br>2                         | 91       | 0.3                             | 13 | 0.3                              | 13        |

| 14       | VSS-M4S        | 1.7<br>0                           | 80<br>0 | 1.6<br>0                              | 51<br>1 | 0.7<br>8                             | 29<br>6   | 0.6                             | 71   | 0.8<br>2                         | 91       | 0.3                             | 13 | 0.3                              | 13        |

| 15       | VSS-<br>M2SM4S | 1.8<br>0                           | 81<br>3 | 1.6<br>0                              | 51<br>1 | 0.7<br>8                             | 29<br>6   | 0.6<br>3                        | 71   | 0.8<br>2                         | 91       | 0.3<br>1                        | 13 | 0.3<br>1                         | 13        |

| 16 | QB - M3D | 1.8<br>0 | 81<br>3 | 1.2<br>0 | 39<br>2  | 0.7 | 29<br>6 | 0.6 | 71 | $\begin{vmatrix} 0.8\\2 \end{vmatrix}$ | 91 | 0.3 | 13 | 0.3 | 13 |

|----|----------|----------|---------|----------|----------|-----|---------|-----|----|----------------------------------------|----|-----|----|-----|----|

|    |          | -        | -       | -        |          |     |         |     |    |                                        |    | -   |    |     |    |

| 17 | QB - M4D | 1.8      | 81      | 1.3      | 44       | 0.7 | 29      | 0.6 | 71 | 0.8                                    | 91 | 0.3 | 13 | 0.3 | 13 |

| 17 |          | 0        | 3       | 0        | 4        | 8   | 6       | 3   | /1 | 2                                      |    | 1   | 15 | 1   | 15 |

| 18 | QB_M3D   | 1.7      | 80      | 0.7      | 0.7 75 0 | 0.7 | 29      | 0.6 | 70 | 0.7                                    | 87 | 0.3 | 13 | 0.3 | 13 |

| 10 | M4D      | 0        | 3       | 0        | 15       | 8   | 6       | 0   | /0 | 7                                      | 07 | 1   | 15 | 1   | 15 |

| 19 | OD MIC   | 1.6      | 79      | 1.5      | 37       | 0.7 | 29      | 0.6 | 71 | 0.8                                    | 01 | 0.3 | 13 | 0.3 | 12 |

| 19 | QB_M1G   | 0        | 3       | 0        | 5        | 8   | 6       | 3   | /1 | 2                                      | 91 | 1   | 15 | 1   | 13 |

| 20 | OD MOC   | 1.8      | 81      | 1.4      | 36       | 0.7 | 29      | 0.6 | 71 | 0.8                                    | 91 | 0.3 | 13 | 0.3 | 13 |

| 20 | QB_M2G   | 0        | 3       | 0        | 2        | 8   | 6       | 3   | 71 | 2                                      | 91 | 1   | 13 | 1   |    |

| 21 | QB_M1G   | 1.7      | 80      | 1.3      | 23       | 0.7 | 29      | 0.6 | 71 | 0.8                                    | 91 | 0.3 | 13 | 0.3 | 13 |

| 21 | M2G      | 0        | 3       | 0        | 9        | 8   | 6       | 3   | /1 | 2                                      | 91 | 1   | 15 | 1   | 15 |

| 22 | M1G_M2   | 1.6      | 79      | 1.3      | 23       | 0.7 | 29      | 0.6 | 71 | 0.8                                    | 91 | 0.3 | 13 | 0.3 | 12 |

|    | G        | 0        | 3       | 0        | 9        | 8   | 6       | 3   | 71 | 2                                      | 91 | 1   | 15 | 1   | 13 |

| 23 | M3G_M4   | 1.3      | 25      | 1.5      | 49       | 0.7 | 29      | 0.6 | 71 | 0.8                                    | 91 | 0.3 | 13 | 0.3 | 13 |

| 23 | G        | 0        | 7       | 0        | 8        | 8   | 6       | 3   | /1 | 2                                      | 91 | 1   | 15 | 1   | 15 |

| 24 | BLB -    | 1.8      | 80      | 1.5      | 49       | 0.7 | 29      | 0.6 | 71 | 0.8                                    | 91 | 0.3 | 13 | 0.3 | 13 |

| 24 | M6S      | 0        | 5       | 0        | 8        | 8   | 6       | 3   | /1 | 2                                      | 91 | 1   | 15 | 1   | 15 |

| 25 | WL-      | 1.8      | 81      | 1.5      | 49       | NA  | NA      | 0.6 | 70 | 0.7                                    | 87 | 0.3 | 13 | 0.3 | 13 |

|    | M5GM6G   | 0        | 3       | 0        | 8        | INA | INA     | 0   | /0 | 7                                      | 0/ | 1   | 15 | 1   | 13 |

### 5. Conclusion:

Fault, fault model, and fault coverage with minimal test latency against the technology variation are the three major concerns of the testing embedded SRAM. In this paper, we implemented a new test technique for embedded SRAMs using a parasitic extraction method for obtaining maximum defect coverage for short and open defects. Using three levels of technologies 45nm, 32nm, and 7 nm, the fault models are developed the overall fault models developed using all the technologies are 72 for short defects and 75 for open defects as shown in table 2 and table 3 respectively. Using the proposed method we found existing fault models such as SAF, UWF, URF, TF, NAF, etc., along with an undetectable fault named an Undefined Short Fault. To implement this we used Microwind 3.9 simulation tool. The proposed parasitic test technique provides 100% fault coverage for static and dynamic faults including a few undetectable faults for single-cell SRAM. At the same time, the test method provides a fault dictionary at each technology level under consideration. Based on this fault dictionary, identifies equivalent faults and unique faults at each technology with 100% fault coverage, which cannot be seen with other existing techniques. **References:**

[1] R.Dekker, F. Beenker, and L. Thijssen, "A realistic Fault Model and Test Algorithms for Static Random Access Memory," IEEE Transactions on Computer-Aided Design, VOL 9, June 1990.

- [2] M.Venkatesham, S. K.Sinha and M. Parvathi, "Study on Paradigm of Variable Length SRAM Embedded Memory Testing" Proceedings of the Fifth International Conference on Electronics, Communication and Aerospace Technology (ICECA) 2021.

- [3] S.Manoj and J.Pineda de Gyvez, "Defect-Oriented Testing for Nano-Metric CMOS VLSI Circuits", Frontiers in Electronic Testing (FRET, volume 34), Springer-2007.N.A. Zakaria, W.Z.W. Hasan, I.A. Halin, R.M Sidek, Xiaoqing Wen, "Fault Detection with Optimum March Test Algorithm" 3rd International Conference on Intelligent Systems Modelling and Simulation, 2012.

- [4] D.Niggemeyer, M.Redeker, and J.Otterstedt "Integration of Non-classical Faults in Standard March Tests," Proceedings. International Workshop on Memory Technology, Design and Testing, Aug-1998.

- [5] A.Benso, A.Bosio, S.Di Carlo, G.Di Natale and P.Prinetto, "Automatic March Tests Generations for Static linked faults in SRAMs" IEEE Proceedings of the Design Automation & Test in Europe Conference, 2006.

- [6] S.Hamdioui, Z. Al-Ars, and A.J.V de Goor, "Testing Static and Dynamic Faults in Random Access Memories", Proceedings 20<sup>th</sup> IEEE VLSI Test Symposium (VTS) 2002.

- [7] H. Balachandran, D. M. H. Walker "Improvement of SRAM-based failure analysis using calibrated Iddq testing" IEEE 14<sup>th</sup> VLSI Test Symposium, 1996, pp. 130 – 136

- [8] M. Sachdev, "Open Defects in CMOS RAM Address Decoders", IEEE Design & Test of Computers, vol.14, n.2, Apr-Jun 1997, pp. 26-33.

- [9] M.Parvathi, N.Vasantha, K. Satya Parasad, "Fault Model Anlysis by Parasitic Extrction Method for Embedded SRAM" International Journal of Research in Engineering and Technology (IJRET), 2013.

- [10] M.Parvathi, K.Satya Prasad, N. Vasantha, "Testing of Embedded SRAMs Using Parasitic Extraction Method" 9th International Conference on Robotic, Vision, SignalProcessing and Power Applications, 398,(2017).

- [11] M.Venkatesham, S.K.Sinha and M Parvathi "Analysis of Open Defect Faults in Single 6T SRAM Cell Using R and C Parasitic Extraction Method", IEEE International Conference on Disruptive Technologies for Multi-Disciplinary Research and Applications (CENTCON-2021) pp.213-217, 2021.

- [12] C.James, M. Li, C.W.Tseng, and E.J. McCluskey, "Testing for Resistive Opens and Stuck Opens", IEEE ITC International Test Conference, 2001.M.Venkatesham, S.K.Sinha and M Parvathi "Extraction of Undetectable Faults in 6T-SRAM Cell", IEEE International Conference on Communication, Control and information Sciences(ICCISc),pp.13-17, 2021.

- [13] L.Dilillo, P.Girard, S.Pravossoudovitch and A.Virazel, "Comparison of Open and Resistive-Open Defect Test Conditions in SRAM Address Decoders", IEEE Proceedings of the 12th Asian Test Symposium, 2003

- [14] L.Dilillo, P.Girard, S.Pravossoudovitch and A.Virazel, "Resistive-Open Defects in Embedded-SRAM core cells: Analysis and March Test Solution", 13th Asian Test Symposium, Nov-2006.

- [15] M.Venkatesham, S.K.Sinha and M.Parvathi, "Fault Detection and Analysis in embedded SRAM for sub nanometer technology" International Conference on Applied Artificial Intelligence and computing (ICAAIC) 2022.